在過去較長的一段時間裡,邏輯晶片的電晶體數目一直迅速增長,但製造工藝難度也隨之大幅度提升,且成本越來越高。所以無論是擁有自有晶圓廠的 Intel 還是像台積電這樣的晶片代工廠都在尋求延續摩爾定律。

不久前的一次會議中, Intel 稱摩爾定律還將延續,而近日台積電在官方部落格中也稱,摩爾定律沒有死亡。

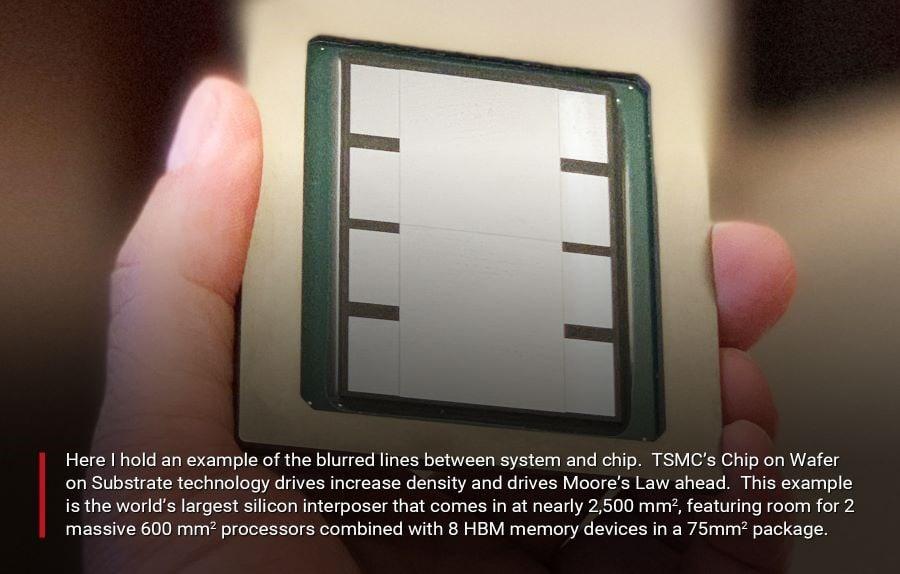

圖片來自台積電

文章稱摩爾定律一直被認為是一種定律,但更可被描述為觀察半導體器件或晶片中電晶體數量的歷史及對未來晶片發展的指導。這種觀察和預測在過去幾十年來基本都是正確的。但由於近些年晶片製程提升緩慢,這也造成了一些人認為摩爾定律死亡。

在這些年晶片的計算性能一直在提升,電晶體的數量也在飛速增長,而通常晶片的Die的大小增長幅度卻沒有如計算性能提升得大,從這也能看出電晶體密度提升的很快。所以台積電在不斷推進2D晶片的單位面積電晶體密度,宣佈了N5P工藝。

但2D晶片製造工藝的提升帶來的晶片電晶體密度提升已經不如以前明顯了,所以台積電想通過多層堆疊和先進封裝技術來解決未來的計算設備的問題。

台積電想要通過提升系統級密度來滿足當前人工智慧和高性能計算的性能需求:透過先進封裝工藝將高速記憶體和計算內核封裝在一起,以達到降低延遲、功耗並提升整體性能的目標。而通過多層堆疊的途徑也可以大幅提升晶片的電晶體密度。

加入 Intel 的著名晶片設計師Jim Keller在不久前的Silicon 100中也有相同的看法,在目前2D晶片製造工藝接近物理極限的情況下,大家也算是殊途同歸了。

沒有留言:

張貼留言